一文看懂芯片的设计流程

芯片分为数字芯片、模拟芯片、数模混合芯片等多种类别。不同类别的设计流程也存在一些差异。接下来,我们就以数字芯片为例,详细看看芯片到底是如何设计出来的。

免费影视、动漫、音乐、游戏、小说资源长期稳定更新! 👉 点此立即查看 👈

芯片分为数字芯片、模拟芯片、数模混合芯片等多种类别。不同类别的设计流程也存在一些差异。

接下来,我们就以数字芯片为例,详细看看芯片到底是如何设计出来的。

芯片设计的主要流程

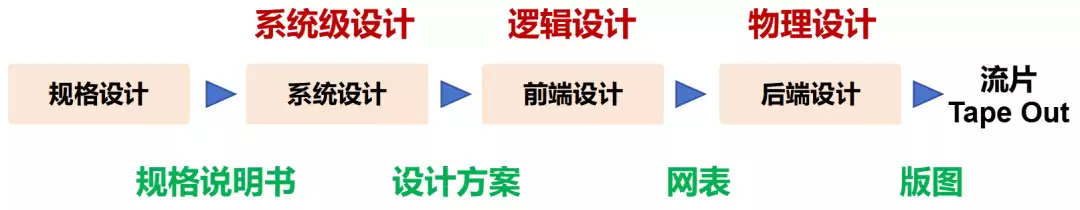

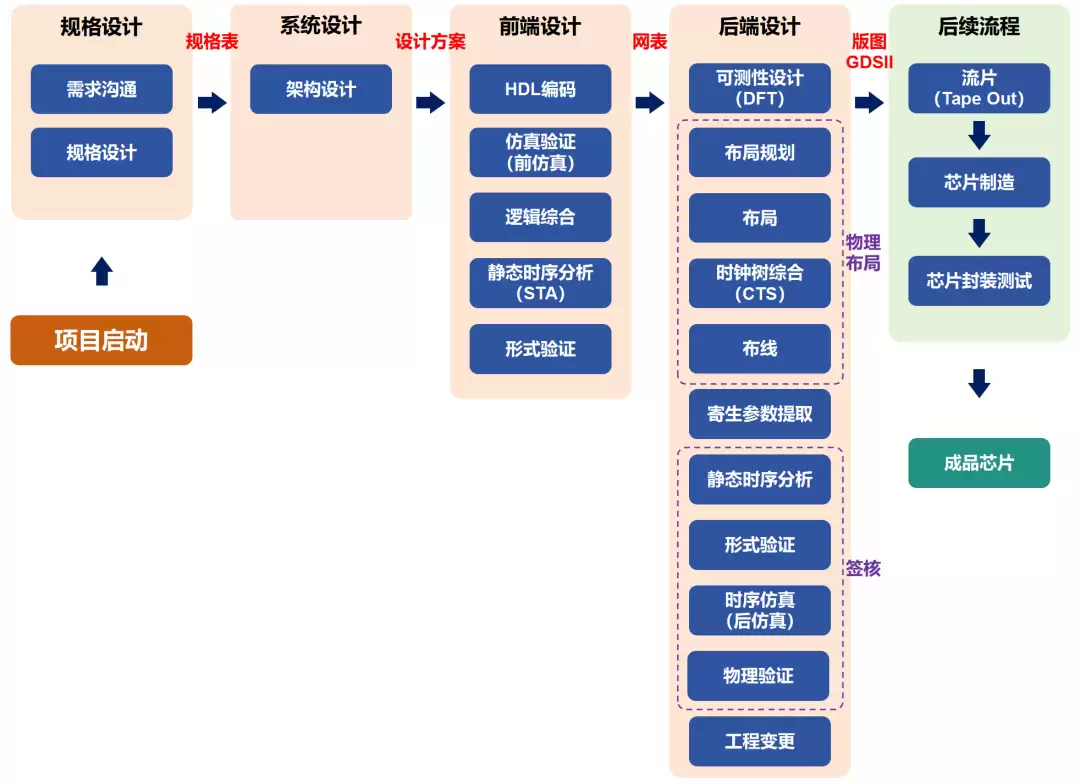

芯片的设计,总体分为规格定义、系统设计、前端设计(Front-End Design)和后端设计(Back-End Design)四个阶段。

图片

图片

网上有些资料为了简单,也会将规格定义和系统设计也归入前端设计。

上篇文章小枣君给大家说过,现在主流的芯片设计思路是自顶向下(Top-Down),也就是“先宏观,再微观”。

图片

图片

简单来说,就是先做芯片整体设计(功能、接口、模块),再做各个模块的设计。做模块设计的时候,先设计逻辑原理(写代码),然后再用EDA工具转化为逻辑电路图(网表),最后再设计物理电路图(版图)。

整个过程,穿插着大量的“设计-验证(仿真)-设计-验证(仿真)”循环。需要确保每一步都准确无误,才会进入下一步。

四大阶段中,前端设计,就是逻辑设计。主要是将芯片的功能需求转化为可实现的电路逻辑,确保功能正确性,不考虑物理实现细节。

后端设计,则是物理设计,专注于物理实现,将前端的设计转化为实际的版图。这个阶段需要脚踏实地,考虑制造工艺约束、信号完整性、功耗管理等实际问题,解决物理实现的工艺挑战。

图片

图片

前端设计和后端设计的各个子阶段如下图所示:

图片

图片

接下来,我们分别进行介绍。

规格定义

芯片设计的第一步,是搞明白自己到底要做一款什么样的芯片。

这不是领导拍脑袋决定的,而是需要芯片设计团队和客户(甲方)以及利益相关方进行充分沟通,了解具体设计需求之后确定的。

需求包括:到底要实现什么功能,用于什么环境,算力、成本、功耗大概是多少,需要提供哪些接口,需要遵循什么安全等级,等等。

所有的需求会转化为芯片的基本参数,最终以Spec(芯片规格说明书)文件的形式进行记录。芯片设计的基本要求,就此确定。

系统设计

接下来,就要由架构工程师出马了。

架构工程师要根据规格Spec,设计具体的实现方案。包括但不限于:整个芯片的架构、业务模块、供电、接口、时序、性能指标、面积和功率约束等。

芯片的架构主要由芯片的类别和功能所决定。

如果芯片主要用于通用计算和数据处理,冯・诺依曼架构可能是一个合适的选择。如果侧重于高速的数据处理和实时性要求高的应用,如数字信号处理或一些特定的嵌入式系统,哈佛架构可能更具优势。

对于复杂的芯片设计,还可能采用多核架构或异构集成架构(混搭)。

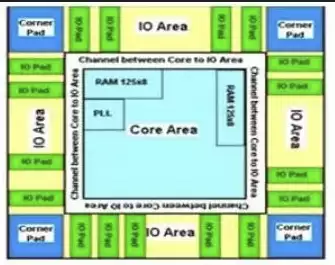

芯片的整体布局(示例)

芯片的整体布局(示例)

选定架构之后,架构师还要在细节上进行优化和创新。例如调整各个功能模块之间的连接方式、优化数据通路以减少延迟,或者采用新的计算模式,等等。

架构师还要确定哪些功能可以用软件实现,哪些部分需要用硬件实现。上篇小枣君介绍过IP核,哪些部分要采购IP核,哪些部分自己做,也是由架构师决定的。

前端设计(逻辑设计)

好了,开始进入前端设计部分了。我们保持耐心,一步一步来看。

· HDL编码

首先,是进行HDL(Hardware Description Language,硬件描述语言)编码。

架构设计方案完成后,芯片设计工程师将根据方案,针对各模块进行具体的电路设计。他会使用专门的硬件描述语言(Verilog或VHDL),对具体的电路实现进行RTL(Register Transfer Level,寄存器传输级)级别的代码描述。

简单来说,就是用代码来表述芯片的逻辑功能和数据传输。

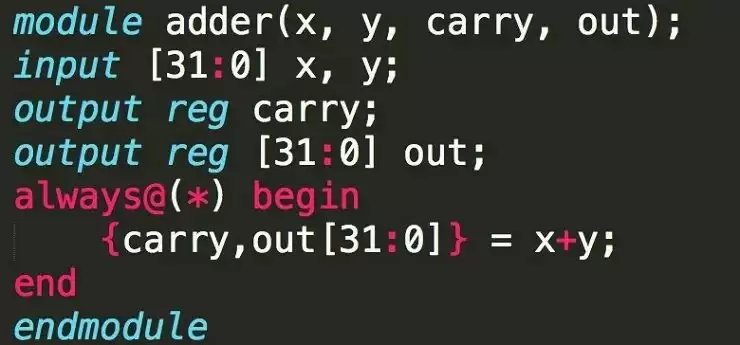

Verilog作为一种常用的硬件描述语言,能够对电路(系统)进行多层次描述,包括系统级、算法级、寄存器传输级(RTL级)、门级和开关级。在数字IC设计流程中,RTL级描述最为关键和常用。因此,Verilog代码也常被称作RTL代码。

Verilog代码范例(32位加法器)

Verilog代码范例(32位加法器)

需要注意的是,HDL编码需要结合晶圆厂提供的库(libaray)和器件(device)等基础资源来设计。有些芯片设计工程师也会基于晶圆厂提供的资源,进行底层优化设计。

·仿真验证

HDL编码完成之后,就要开始第一波验证(Verification)了。

前面我说过,芯片设计几乎每一步都要进行验证或仿真,就是为了确保不出错,因为出错的代价实在太大。

这一步的仿真验证,主要包括电路逻辑功能方面的验证,也就是证明设计的功能是否符合设计规格中的定义,是否存在逻辑实现错误。

如果发现错误,就需要返回上一步,进行修改,甚至要返回方案设计阶段进行修改。修改之后,再重新进行验证。

验证方法包括:(借助工具)通过在搭建的验证环境中输入激励(就是加输入信号),然后看检测输出波形是否和预期一样,以此来进行判断。

验证仿真的工具主要包括VCS、Qustasim等EDA工具(进行编译和仿真),以及Verdi等工具(进行debug)。

需要注意的是,这个阶段的仿真,也被称为“前仿真”。待会我们还有一个“后仿真”。

“前仿真”是在理想状态下进行的。它基于理想化的抽象模型,忽略物理延迟和布线细节,专注于功能正确性。

·逻辑综合

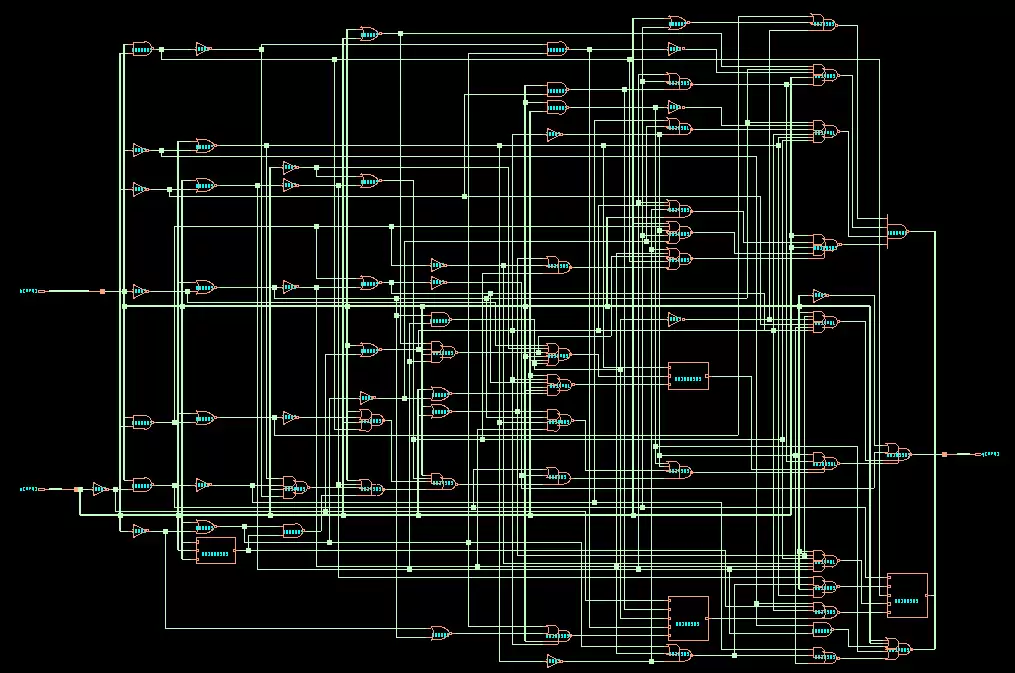

接下来,验证工程师要使用一些EDA工具,将RTL代码翻译成门级网表(Gate levelNetlist),也就是实际的逻辑门电路(也包含了逻辑结构和连接关系,也是后端设计的关键输入)。

门级网表的样例

门级网表的样例

这个步骤就是逻辑综合(Synthesis),有时候直接简称“综合”。

逻辑综合主要包括翻译、优化、映射步骤。

翻译:先将Verilog/VHDL代码转换为工艺无关的、初级的、未优化的通用门级电路。

优化:逻辑综合需要设定约束条件,也就是希望逻辑综合出来的电路在面积、时序、时延等(PPA)目标参数上达到的标准。优化,是根据约束条件和工艺库(由晶圆厂提供)参数,进行逻辑结构调整,去掉冗余单元,以此满足要求。

映射:最终,将门级逻辑电路映射到的工艺库上。

需要注意的是,不同晶圆厂的工艺库,门电路基本标准单元(standard cell)的面积、时序参数是不一样的。所以,选用的库不一样,综合出来的电路在面积、时序上就不一样。

·静态时序分析

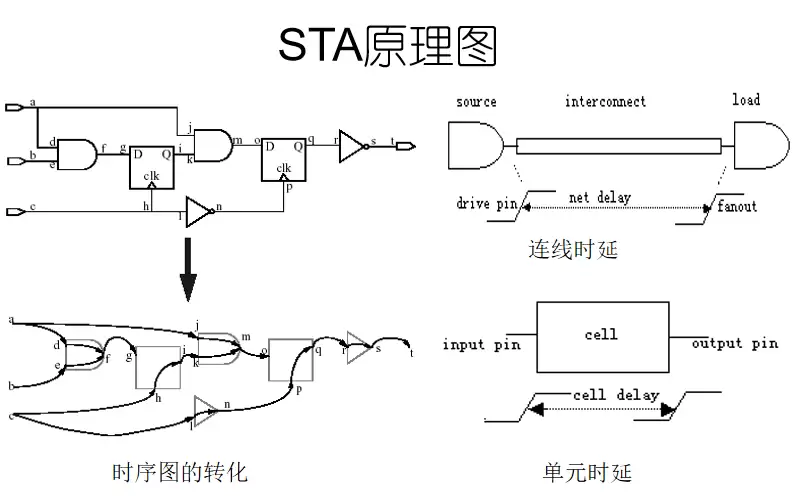

静态时序分析(Static Timing Analysis,STA),也属于验证的范畴,主要是在时序上对电路进行验证。

具体来说,是在不提供激励的情况下,验证设计时序特性,检查电路是否存在建立时间(setuptime)和保持时间(holdtime)的违例(violation)。

这句话有点难理解,要搞懂它,就要先搞懂时序(timing)。前面我们多次提到时序。芯片时序是集成电路设计中确保信号传输与时钟同步的关键技术,非常重要。电子设备由时钟信号驱动,如果时序存在问题,各个模块之间的工作节奏就会错乱,影响各个元件以及整个芯片的工作频率,进而影响整体性能。

在数字电路中,一个寄存器如果出现前面说的违例,就无法正确采样数据和输出数据。所以,以寄存器为基础的数字芯片功能,就会出现问题。

静态时序分析(STA)的作用,主要体现在以下几个方面:

首先,它能帮助我们确定芯片的最高工作频率。

通过详细的时序分析,工程师可以更好地控制工程的各个环节,从而减少延迟,尽可能地提升芯片的工作频率。

芯片的最高工作频率由网表(netlist)的关键路径决定。关键路径是网表中信号传播时延的最长路径。

其次,静态时序分析也是检查时序约束是否满足的重要手段。

在时序分析的过程中,我们可以查看目标模块是否满足预设的约束条件。如果不满足,分析结果将帮助我们精确地定位到问题点,并给出详细的改进建议。

最后,静态时序分析还能用于分析时钟质量。

时钟信号存在抖动、偏移和占空比失真等缺陷。通过时序分析,我们可以有效地验证这些缺陷对目标模块性能的影响。

STA工具,包括Synopsys的PT(Prime Time)工具等。

它可以分为三个基本步骤:

1、将netlist看成一个拓扑图;

2、进行时延计算(连线时延net delay、单元时延cell delay);

3、找到关键路径,并计算时延,进行判断。

图片

图片

·形式验证

这一步也是验证,是从功能上对逻辑综合后的网表(netlist)进行验证。

形式验证主要通过数学手段来完成,不考虑工艺因素,无需激励或时序检查即可进行。

在形式验证中,等效性检查(也叫等价性检查)是一种常用方法。

它通过将当前设计与已知的黄金设计(功能验证后的HDL设计)进行对比,来确认设计的功能等效性,确保逻辑综合过程中没有改变原先HDL描述的电路功能。

覆盖率,是评估验证充分性的一个关键指标。它主要分为两大类:代码覆盖率和功能覆盖率。

代码覆盖率,旨在检查RTL代码是否冗余,并确保设计要点得到全面遍历。

功能覆盖率,专注于检查自定义container(容器)中的功能是否被充分测试。

在前端设计的最后阶段,需要完成代码覆盖率的充分性审查。对于未达到100%覆盖率的情况,需要给出合理解释,以确保芯片功能不受影响。

相关攻略

AI 时代最赚钱的公司,可能从来不是做 AI 的那个。作者|张勇毅编辑|靖宇淘金热里最稳赚的人,从来不是淘金的,是卖铲子的。这句老话在 2026 年的科技行业又应验了一次。只不过这次卖铲子的不是英伟

4月5日消息,据报道,iPhone 18 Pro系列除首发台积电2nm工艺的A20 Pro芯片外,还将搭载苹果自研的C2蜂窝网络调制解调器与N2无线网络芯片。iPhone 18 Pro系列的A20

新智元报道编辑:LRST【新智元导读】从「会写Tcl」,到「能真正推进设计优化流程」,大模型正第一次以Agent形态进入真实EDA工具链。大模型正在快速进入工程研发现场。但在 EDA(电子设计自动化

4月1日,OPPO正式推出全新K15 Pro系列智能手机,该机以潮酷设计、主动散热、旗舰性能与长续航为核心亮点,面向电竞玩家、潮流用户与户外爱好者打造全场景体验。据了解,本次发布的K15 Pro系列

根据研调机构Counterpoint报告,当前主流HBM(高带宽内存)采用微凸块(micro-bump)搭配热压键合(TCB)进行芯片连接,目前已实现12至16层堆叠。但随着HBM未来向20层以上堆

热门专题

热门推荐

加密货币行业翘首以盼的监管里程碑,终于有了实质性进展。美国证券交易委员会(SEC)主席保罗·阿特金斯(Paul Atkins)近日证实,那份允许加密项目在早期获得注册豁免权的“安全港”框架提案,已经正式送抵白宫,进入了最终审查阶段。 在范德堡大学与区块链协会联合举办的数字资产峰会上,阿特金斯透露了这

微策略Strategy报告:第一季录得144 6亿美元浮亏 再斥资约3 3亿美元买进4871枚比特币 市场震荡的威力有多大?看看Strategy的最新季报就明白了。根据其最新向美国证管会(SEC)提交的8-K报告,受市场剧烈波动影响,这家公司所持的比特币在第一季度录得了一笔惊人的数字——144 6亿

稳定币巨头Tether的动向,向来是加密世界的风向标。这不,它向Web3基础设施的版图扩张,又迈出了关键一步。公司执行长Paolo Ardoino在社交平台X上透露,其工程团队正在全力“烹制”一个新项目——去中心化搜索引擎 “Hypersearch”。这个消息一出,立刻引发了行业的广泛猜想。 采用D

基地位于Coinbase旗下以太坊Layer2网络Base的Seamless Protocol,日前正式宣告了服务的终结。这个曾经吸引了超过20万用户的原生DeFi借贷协议,在运营不到三年后,终究没能跑赢时间。它主打的核心产品是Integrated Leverage Markets(ILMs)——一

PAAL代币揭秘:深度解析Web3社区治理的核心钥匙 在去中心化自治组织的浪潮中,谁真正掌握了项目的话语权?PAAL代币提供了一套系统化的答案。它不仅是生态内流转的价值媒介,更是开启链上治理大门的核心凭证。通过持有并质押PAAL代币,用户能够对协议升级、资金分配乃至战略方向等关键事务投出决定性的一票